# The Research & Development of an Advanced Verification Infrastructure for ASIC Devices using SystemVerilog & the Verification Methodology Manual (VMM)

In One Volume

Michael Anthony McMahon B.Eng

May 2010

Submitted for the Degree of Master of Engineering

Submitted to: Galway Mayo Institute of Technology, Galway, Ireland

Research carried out at: Chipright LTD, Galway, Ireland

# **Declaration**

| I hereby declare that the work presented in this thesis is my own and that it has not been |

|--------------------------------------------------------------------------------------------|

| previously used to obtain a degree in this institution or elsewhere.                       |

Michael Anthony McMahon

## Statement of Confidentiality

The material contained in this thesis should not be used, sold, assigned, or disclosed to other person(s), organisation(s) or corporation(s) without the written consent of both Chipright Ltd, and Niall O'Keeffe.

Galway Mayo Institute of Technology: Contact: Niall O'Keeffe

Tel: +35391 742057

Email: niall.okeeffe@gmit.ie

Chipright: Contact Kevin Keane

Tel: +91 444168

Email kevin.keane@chipright.com

## **Prologue**

The research described in this thesis has been conducted over a 24-month period as part of a college/industry partnership project. This project was funded under the Innovation Partnership research grants scheme administered by Enterprise Ireland. The aim of the project is to research and develop an Advanced Verification Infrastructure using SystemVerilog and the Verification Methodology Manual (VMM).

#### Acknowledgements

I would like to thank the following people for their support and encouragement during the course of this project.

#### I would like to thank:

First and foremost, my supervisor, Niall O'Keeffe of the Department of Electronic Engineering in GMIT, for his supervision, guidance, inspiration, and his constructive suggestions throughout this research study. Without his support and encouragement this research would not have been done.

Emer O'Mahony for all her help and support throughout the course of my studies.

The senior engineers from Chipright Ltd. for their help and support while doing this project. They were of great help in teaching me to become familiar with SystemVerilog, helping with developing the testbench and giving useful insights into the practical and potential implementations of SystemVerilog.

I would also like to give a special mention to my parents, who have helped and guided me through my time at college in GMIT.

#### **Abstract**

In digital design much of the focus and attention in the past has been towards developing languages and tools primarily for use in designing an ASIC device. Today, the single biggest problem in digital design is the time that is spent in the Verification process. With this in mind the key EDA companies have focused a large proportion of their research and development budgets towards supporting new verification languages and methodologies, namely, SystemVerilog and OpenVera. SystemVerilog is the industry's first unified hardware description and verification language (HDVL). Along with developing SystemVerilog, the EDA companies have developed methodologies to support the language. The two main methodologies are the Synopsys's Verification Methodology Manual and Cadence/Mentor Open Verification Methodology. These methodologies are geared towards the implementation of functional coverage-points; use of assertion based coverage and constrained random test techniques.

This thesis outlines a VMM style test bench architecture that is structured to gain maximum efficiency from both constrained random and directed test case development. This thesis describes how directed and constrained random tests can be implemented inside a reusable directory structure that takes full advantage of the coverage and assertion techniques.

This thesis uses an IEEE-754 compliant floating-point adder model as part of a case study that illustrates a complete set of results extrapolated from using this test bench structure. An Integrated Inter Circuit (I2C) verification component has also been implemented and used to test the reusability of the test bench structure.

This thesis reviews the use of formal verification within the digital design community. Formal methods such as model checking, equivalence checking and deductive reasoning have become increasingly popular verification techniques. These methods are investigated to see if they could be used as alternative verification techniques within the verification environment.

# TABLE OF CONTENTS

| LIST ( | OF FIGURESX                                             |

|--------|---------------------------------------------------------|

| LIST ( | OF TABLESXV                                             |

| СНАР   | TER 1 INTRODUCTION1                                     |

| 1.1    | Thesis Motivation1                                      |

| 1.2    | Thesis Contributions2                                   |

| 1.3    | Thesis Structure3                                       |

| СНАР   | TER 2 REVIEW OF ASIC VERIFICATION TECHNIQUES6           |

| 2.1    | Introduction6                                           |

| 2.2    | The Goal of Verification8                               |

| 2.3    | The ASIC Verification Challenge11                       |

| 2.4    | Functional Verification13                               |

| 2.5    | The Bottleneck in ASIC Verification15                   |

| 2.6    | Conclusion17                                            |

|        | TER 3 CURRENT VERIFICATION LANGUAGES, METHODOLOGIES     |

| 3.1    | Introduction19                                          |

| 3.2    | SystemVerilog19                                         |

| 3.3    | Verilog20                                               |

| 3.4    | OpenVera21                                              |

| 3.5    | History of Verilog and SystemVerilog21                  |

| 3.6    | SystemVerilog Extensions to Verilog 200123              |

| 3.7    | Methodologies and Tools30                               |

| 3.8    | SystemVerilog Growth within the Verification Industry37 |

| 3.9    | Conclusion39                                            |

| CHAP   | TER 4 VMM BASED VERIFICATION ENVIRONMENT40              |

| 4.1    | Introduction40                                          |

| 4.2    | Device Under Test (Floating-point Adder Model)42        |

| 4.3    | Designing a Verification Environment44                  |

| 4.4    | Floating-point Adder Interface45                        |

| 4.5    | Data Class49                                            |

| 4.6    | Bus Functional Model (BFM)54                            |

|   | 4.7   | The Environment                             | .57 |

|---|-------|---------------------------------------------|-----|

|   | 4.8   | Program and Top File                        | .62 |

|   | 4.9   | Testing of Floating-point Adder Model       | .64 |

|   | 4.10  | Conclusions                                 | .70 |

| C | НАРТ  | TER 5 ADVANCED VERIFICATION ENVIRONEMENT    | .72 |

|   | 5.1   | Introduction                                | .72 |

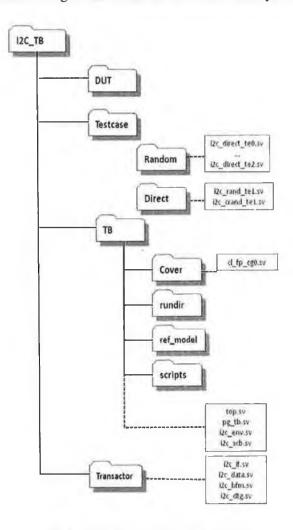

|   | 5.2   | Directory Structure                         | .73 |

|   | 5.3   | Test Bench Architecture                     | .76 |

|   | 5.4   | Reference Model                             | .77 |

|   | 5.5   | Scoreboard                                  | .80 |

|   | 5.6   | Test Case Library                           | .82 |

|   | 5.7   | Functional Coverage                         | .91 |

|   | 5.8   | VMM Planner                                 | .95 |

|   | 5.9   | Testing the Floating-point Adder            | 100 |

|   | 5.10  | Conclusion                                  | 107 |

| ( | СНАРТ | TER 6 ADVANCED BFM (I2C)                    | 109 |

|   | 6.1   | Introduction                                | 109 |

|   | 6.2   | History of I2C                              | 109 |

|   | 6.3   | I2C Bus Hardware                            | 111 |

|   | 6.4   | I2C Bus Protocol                            | 112 |

|   | 6.5   | Building the I2C Environment                | 122 |

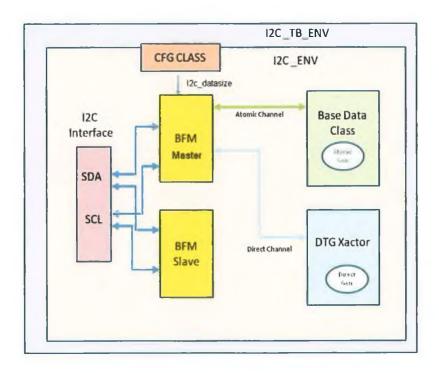

|   | 6.6   | Building the I2C Testbench                  | 123 |

|   | 6.7   | Building the I2C Bus Functional Model (BFM) | 126 |

|   | 6.8   | Master BFM                                  | 127 |

|   | 6.9   | Slave BFM                                   | 131 |

|   | 6.10  | State Machine for BFMs                      | 132 |

|   | 6.11  | Further Implementation of I2C Protocol      | 137 |

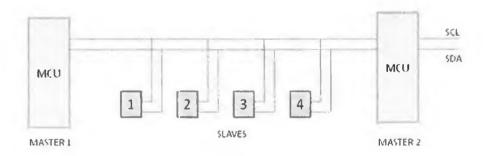

|   | 6.12  | Multi Master Features                       | 139 |

|   | 6.13  | Testing of I2C Protocol                     | 143 |

|   | 6.14  | Conclusion                                  | 149 |

| ( | СНАРТ | TER 7 FORMAL VERIFICATION                   | 151 |

|   | 7.1   | Introduction                                | 151 |

|   | 7.2   | What is Formal Verification?                | 151 |

|   | 7.3   | Why Formal Verification?                    | 153 |

| 7.4   | History of Formal Verification          | 154 |

|-------|-----------------------------------------|-----|

| 7.5   | Deductive Reasoning                     | 156 |

| 7.6   | Model Checking                          | 161 |

| 7.7   | Equivalence Checking                    | 168 |

| 7.8   | Formal Verification and Assertions      | 173 |

| 7.9   | Formal Verification Tools               | 175 |

| 7.10  | Future Trends of Formal Verification    | 176 |

| 7.11  | Conclusion                              | 177 |

| CHAP' | TER 8 CONCLUSION AND FUTURE WORK        | 178 |

| 8.1   | Thesis Summary                          | 178 |

| 8.2   | Conclusions                             | 180 |

| 8.3   | Further Development                     | 181 |

| REFEI | RENCES                                  | 183 |

| APPE  | NDIX 1 PUBLICATION                      | 188 |

| APPE  | NDIX 2 FUNCTIONAL COVERAGE COVER GROUPS | 194 |

| APPE  | NDIX 3 AXIOMS IN DEDUCTIVE REASONING    | 198 |

| APPEN | NDIX 4 MODEL CHECKING TYPES             | 199 |

# List of Figures

| Figure 1.1 Thesis Structure                                                     | 3  |

|---------------------------------------------------------------------------------|----|

| Figure 2.1 Specification Hierarchy                                              | 9  |

| Figure 2.2 Functional Verification of the RTL with respect to the specification | 13 |

| Figure 2.3 Testbench interaction with DUT                                       | 14 |

| Figure 3.1 Timeline of Verilog and SystemVerilog development                    | 22 |

| Figure 3.2 Example of Immediate Assertion                                       | 27 |

| Figure 3.3 Example of Concurrent Assertions                                     | 28 |

| Figure 3.4 VMM Standard Library                                                 | 32 |

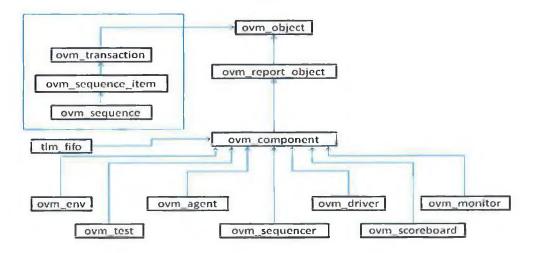

| Figure 3.5 OVM Library                                                          | 34 |

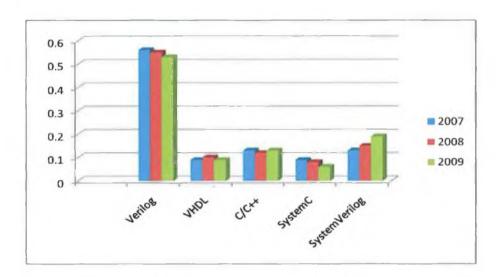

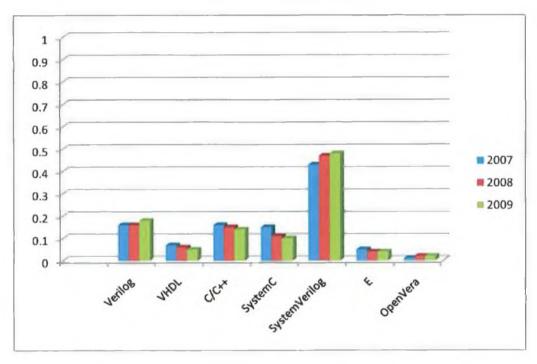

| Figure 3.6 Design language usage                                                | 37 |

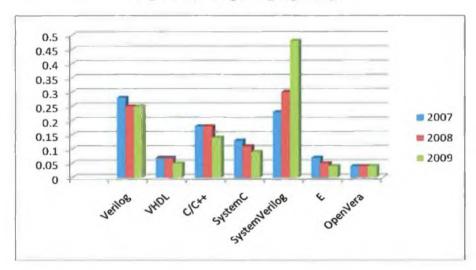

| Figure 3.7 Verification language usage                                          | 37 |

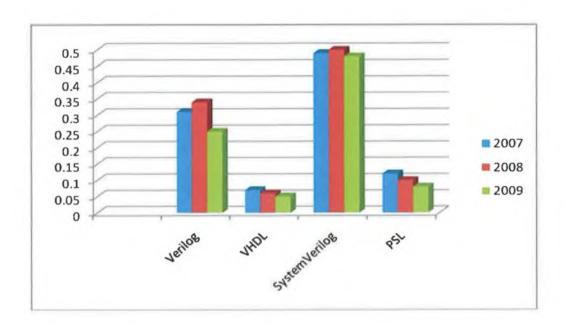

| Figure 3.8 Assertions language usage                                            | 38 |

| Figure 3.9 Predicted verification language engineers usage                      | 38 |

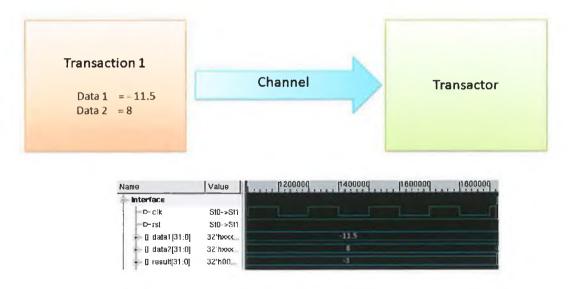

| Figure 4.1 Example of a Floating-point Transaction                              | 40 |

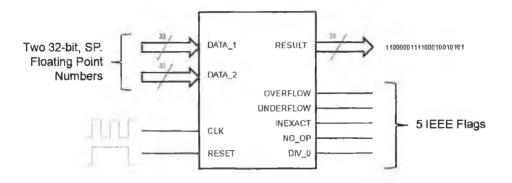

| Figure 4.2 Single Precision Floating-point Adder Model                          | 42 |

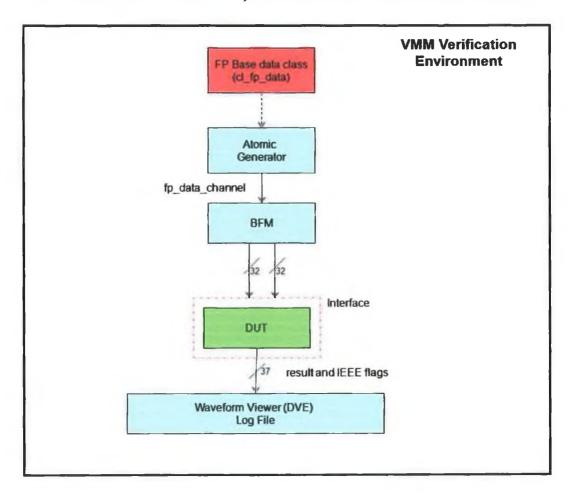

| Figure 4.3: Basic Verification Environment                                      | 44 |

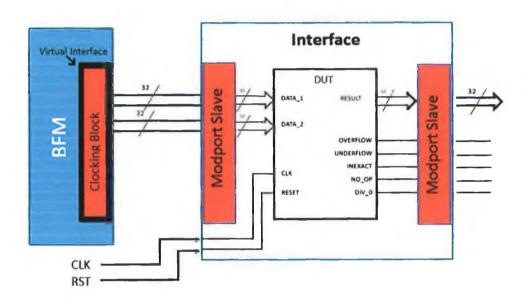

| Figure 4.4 Interface for Floating-point Adder Testbench                         | 45 |

| Figure 4.5 Declaring Clock and Reset                                            | 45 |

| Figure 4.6 Declarations of Signals                                              | 46 |

| Figure 4.7 Modports within Interface                                            | 46 |

| Figure 4.8 Clocking blocks                                                      | 47 |

| Figure 4.9 Example of a SystemVerilog Assertion                                 | 48 |

| Figure 4.10 Data class                                                          | 49 |

| Figure 4.11 Declaring Data 1 and Data 2                                         | 49 |

| Figure 4.12 Declaring VMM log                                                   | 50 |

| Figure 4.13 Allocate Method                                                     | 50 |

| Figure 4.14 ps_display() method                                                 | 50 |

| Figure 4.15 Copy Method                                                         | 51 |

| Figure 4.16 vmm_channel                                                         | 51 |

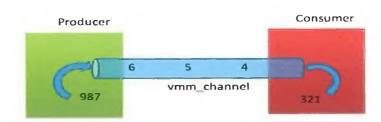

| Figure 4.17 Creating Data Channel                                               | 52 |

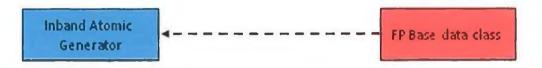

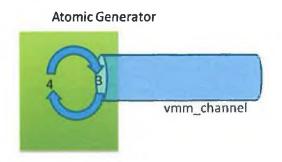

| Figure 4.18 Atomic Generator           | 2 |

|----------------------------------------|---|

| Figure 4.19 Creating Atomic Generator5 | 3 |

| Figure 4.20 Constraint5                | 3 |

| Figure 4.21 Constraining Sign5         | 3 |

| Figure 4.22 vmm_xactor constructor5    | 5 |

| Figure 4.23 do_master task5            | 6 |

| Figure 4.24 The Simulation Flow5       | 7 |

| Figure 4.25 gen_cfg' method5           | 8 |

| Figure 4.26 build method ()5           | 8 |

| Figure 4.27 reset_dut() method5        | 8 |

| Figure 4.28 cfg_dut method5            | 9 |

| Figure 4.29 start method5              | 9 |

| Figure 4.30 wait for end () method6    | 0 |

| Figure 4.31 stop method ()6            | 0 |

| Figure 4.32 cleanup () method          | 1 |

| Figure 4.33 report () method           | 1 |

| Figure 4.34 Program File               | 2 |

| Figure 4.35 Top Module                 | 3 |

| Figure 4.36 Constraint and Assertions  | 4 |

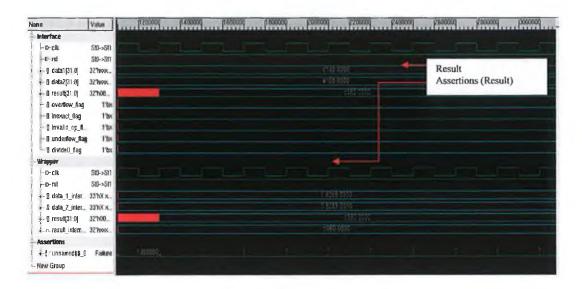

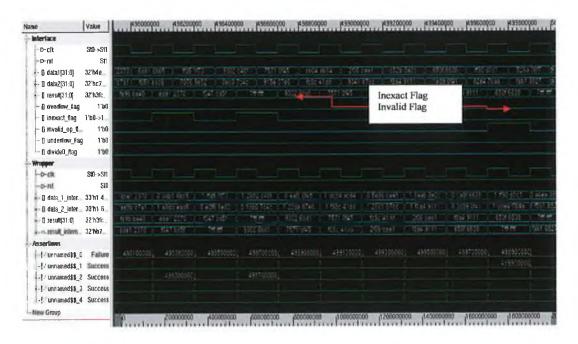

| Figure 4.37 Output Testcase 1          | 5 |

| Figure 4.38 Invalid Flag6              | 5 |

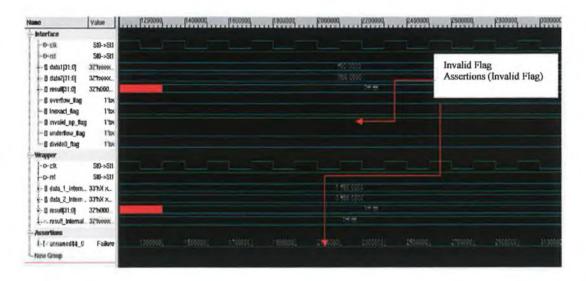

| Figure 4.39 Output Testcase 2          | 6 |

| Figure 4.40 Adding Infinity Numbers    | 6 |

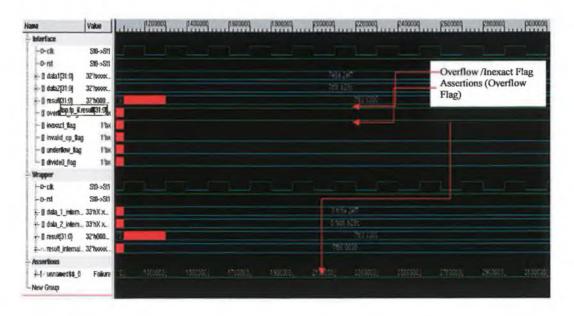

| Figure 4.41 Output Testcase 36         | 7 |

| Figure 4.42 Overflow Flag6             | 7 |

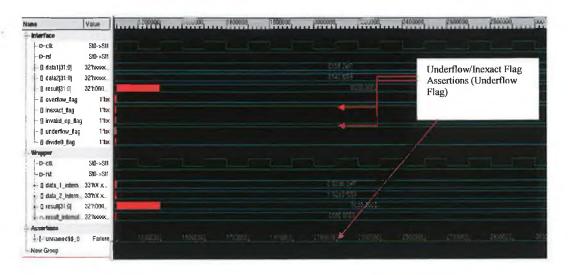

| Figure 4.43 Output Testcase 4          | 8 |

| Figure 4.44 Underflow Flag             | 8 |

| Figure 4.45 Output Testcase 56         | 9 |

| Figure 4.46 Output Testcase 66         | 9 |

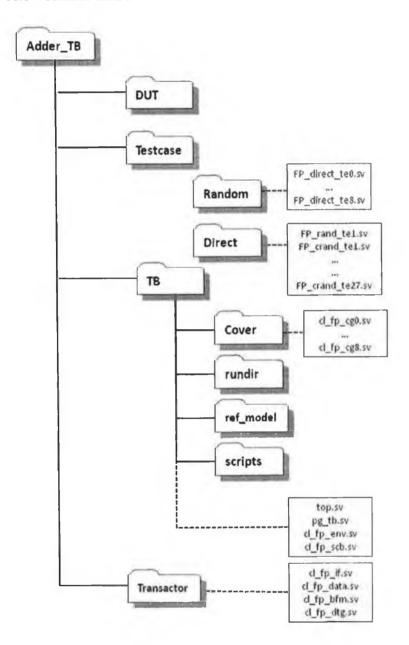

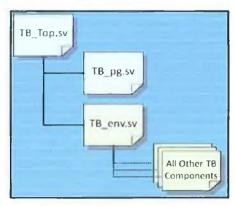

| Figure 5.1 Directory Structure         | 3 |

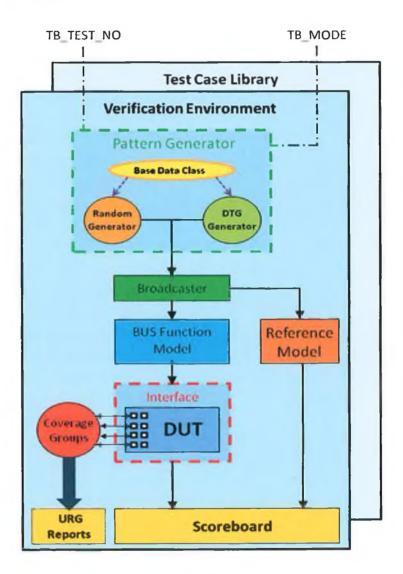

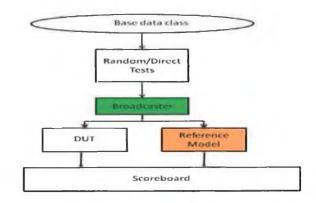

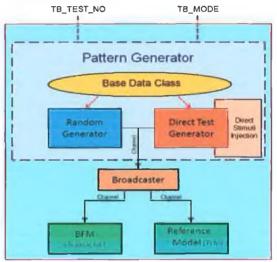

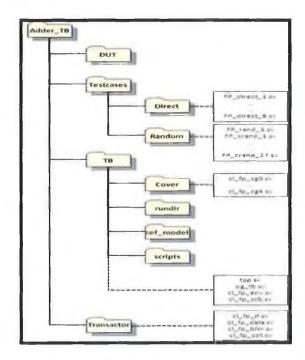

| Figure 5.2 Test Bench Architecture     | 6 |

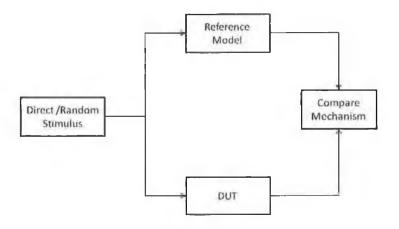

| Figure 5.3 Traditional Reference model | 7 |

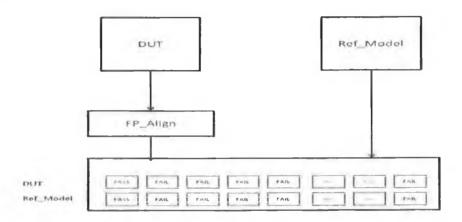

| Figure 5.4 Outputting results from Reference Model                     | .79          |

|------------------------------------------------------------------------|--------------|

| Figure 5.5 Reference Model within the Test Bench                       | 79           |

| Figure 5.6 Connecting up Reference model within Test bench Environment | 79           |

| Figure 5.7 Scoreboard                                                  | 80           |

| Figure 5.8 Compare Mechanisms within Scoreboard                        | 80           |

| Figure 5.9 Outputs from Fail log File                                  | 81           |

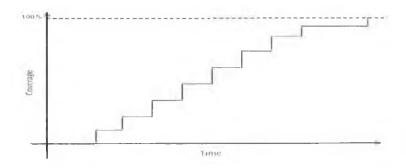

| Figure 5.10 Directed Test Progress                                     | 82           |

| Figure 5.11 Directed Test Coverage                                     | 83           |

| Figure 5.12 Coverage Path                                              | 84           |

| Figure 5.13 Test Case Mechanisms                                       | 85           |

| Figure 5.14 Testcase extends the environment                           | 86           |

| Figure 5.15 Testcase build method                                      | 86           |

| Figure 5.16 Random and Direct Testcase                                 | 87           |

| Figure 5.17 wait_for_end method.                                       | 88           |

| Figure 5.18 Constraint within fp_data_common                           | .88          |

| Figure 5.19 Chosen constrained random/directed stimuli                 | 90           |

| Figure 5.20 Example of a cover group                                   | , 94         |

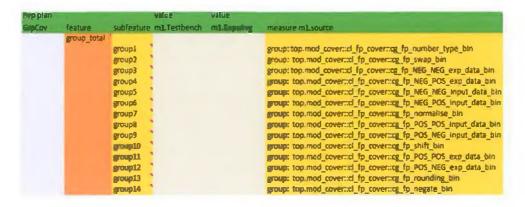

| Figure 5.21 VMM Planner                                                | ,96          |

| Figure 5.22 XML file before being annotated                            | .97          |

| Figure 5.23 Annotated XML File                                         | .98          |

| Figure 5.24 Output from URG Dash Board                                 | 00           |

| Figure 5.25 Output of URG (Group List)                                 | 01           |

| Figure 5.26 Output from URG Dash Board                                 | l <b>02</b>  |

| Figure 5.27 Output of URG (Group List)                                 | 03           |

| Figure 5.28 Show the final Output from VMM planner                     | 03           |

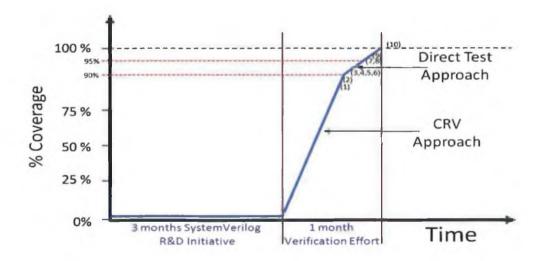

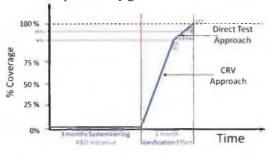

| Figure 5.29 R&D of Verification Environment                            | l <b>0</b> 7 |

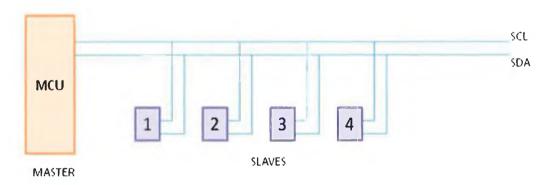

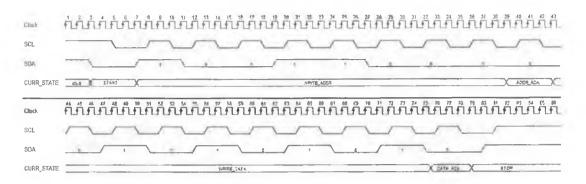

| Figure 6.1 Master communicating with Slave                             | l 12         |

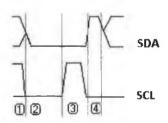

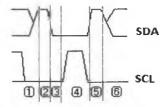

| Figure 6.2 Master Write with Slave Acknowledge                         | l 14         |

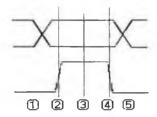

| Figure 6.3 No Acknowledge                                              | 17           |

| Figure 6.4 Repeated Start Condition                                    | 118          |

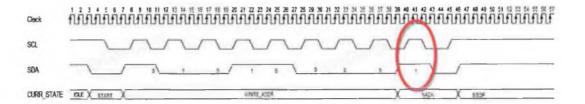

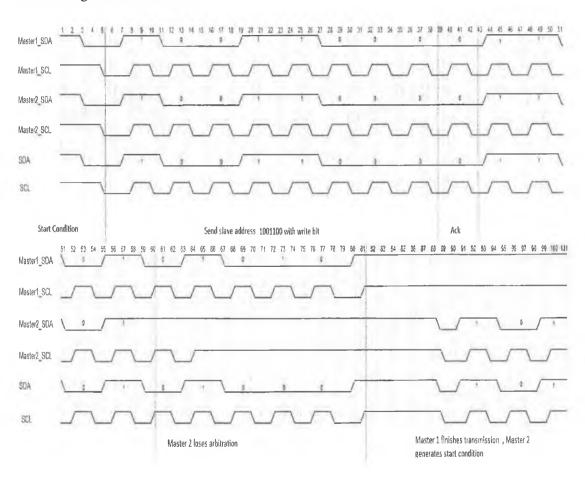

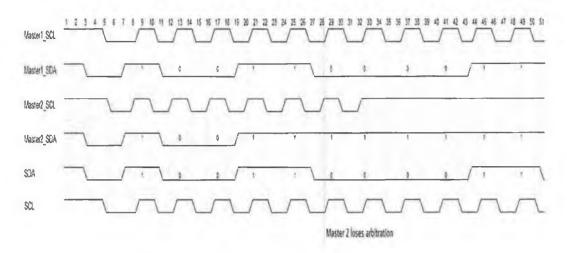

| Figure 6.5 I2C Multi Master Arbitration                                | 18           |

| Figure 6.6 I2C Multi Master Arbitration                                | 119          |

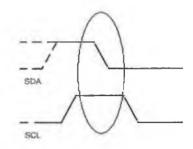

| Figure 6.7 Mulit Master Clock Synchronisation               | 121 |

|-------------------------------------------------------------|-----|

| Figure 6.8 I2C testbench Structure                          | 122 |

| Figure 6.9 12C Interface                                    | 124 |

| Figure 6.10 Data and Address declared within data file      | 124 |

| Figure 6.11 Build method within environment                 | 125 |

| Figure 6.12 Top File                                        | 125 |

| Figure 6.13 Block Diagram of Basic I2C Test bench           | 126 |

| Figure 6.14 Generating Start condition                      | 127 |

| Figure 6.15 Start Condition                                 | 127 |

| Figure 6.16 Sending Address Data                            | 128 |

| Figure 6.17 Slave Address with Acknowledge                  | 128 |

| Figure 6.18 Checking for Acknowledge                        | 128 |

| Figure 6.19 Stop Condition                                  | 129 |

| Figure 6.20 Repeated Start Condition                        | 130 |

| Figure 6.21 Generating SCL Clock                            | 130 |

| Figure 6.22 Acknowledge                                     | 131 |

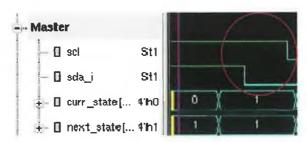

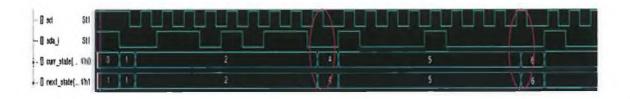

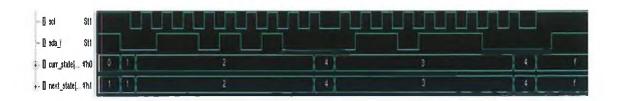

| Figure 6.23 Master FSM                                      | 133 |

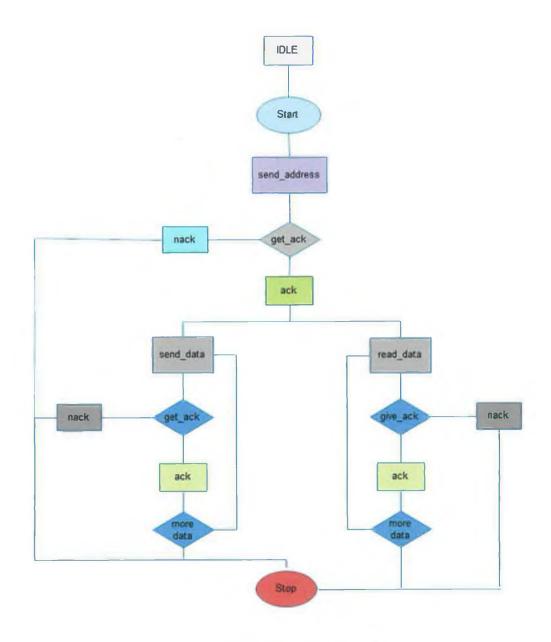

| Figure 6.24 Slave FSM                                       | 134 |

| Figure 6.25 Master and Slave states & control bits          | 135 |

| Figure 6.26 State Machine (Start state)                     |     |

| Figure 6.27 Implementing State Machine and selecting states | 136 |

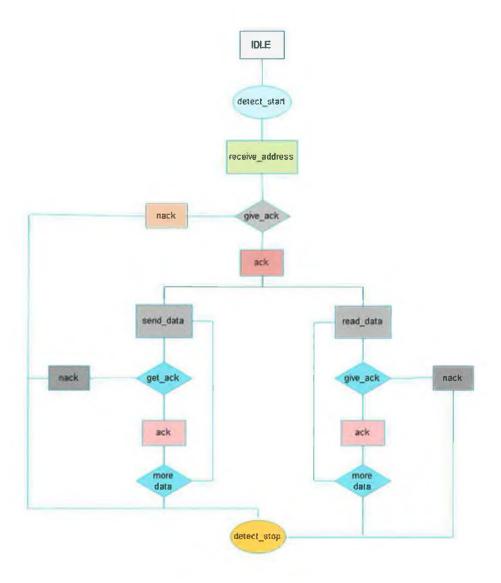

| Figure 6.28 Complete Block Diagram of I2C Testbench         | 137 |

| Figure 6.29 Configuration selection                         | 138 |

| Figure 6.30 Arbitration                                     | 140 |

| Figure 6.31 Checking the SDA line                           | 140 |

| Figure 6.32 Clock Synchronisation                           | 141 |

| Figure 6.33 Low Count off                                   |     |

| Figure 6.34 High count off                                  | 142 |

| Figure 6.35 Start Condition                                 |     |

| Figure 6.36 Test BFM Functionality (Acknowledge)            | 144 |

| Figure 6.37 Test BFM functionality (No Acknowledge)         |     |

| Figure 6.38 Slave write                                     |     |

| Figure 6.39 Repeated Start Condition                              | 144 |

|-------------------------------------------------------------------|-----|

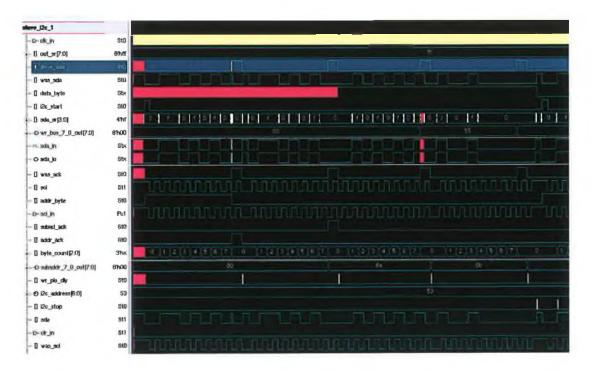

| Figure 6.40 Integrated BFM                                        | 145 |

| Figure 6.41 Slave Core                                            | 145 |

| Figure 6.42 Master Core                                           | 146 |

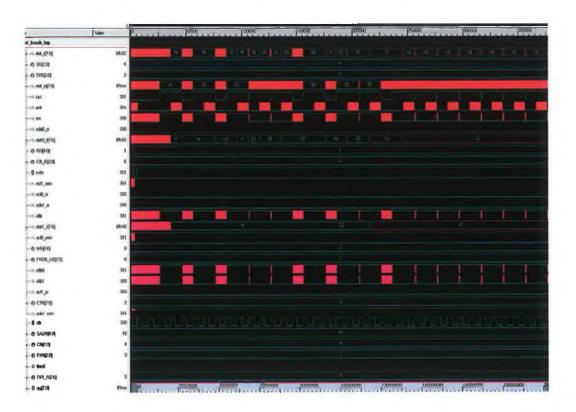

| Figure 6.43 Multi Master Arbitration                              | 147 |

| Figure 6.44 Clock Synchronisation                                 | 148 |

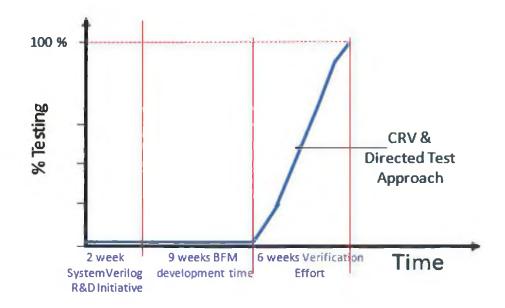

| Figure 6.45 I2C BFM Development time                              | 150 |

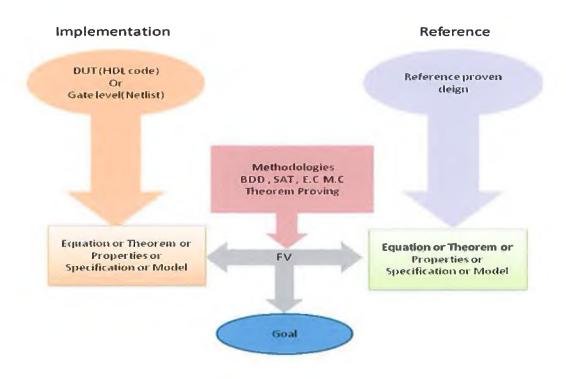

| Figure 7.1 Formal Verification                                    | 152 |

| Figure 7.2 Implementing Deductive Reasoning                       | 157 |

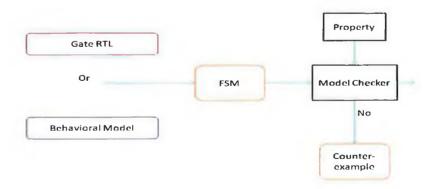

| Figure 7.3 Model Checking                                         | 161 |

| Figure 7.4 State transition graph of Kripke Model                 | 163 |

| Figure 7.5 Infinite Computation Tree                              | 164 |

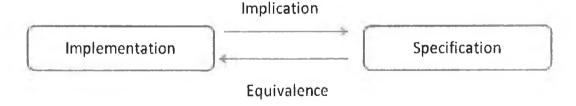

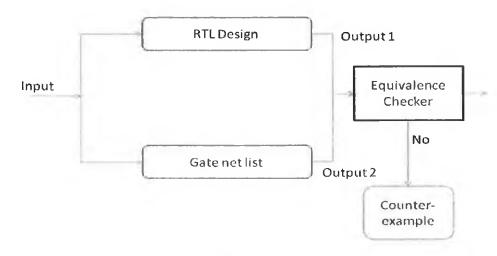

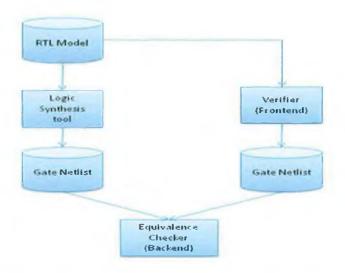

| Figure 7.6 Equivalence Checking                                   | 169 |

| Figure 7.7 Equivalence check of a RTL model against gate net list | 172 |

| Figure 7.8 Assertions used in floating-point adder                | 174 |

# List of Tables

| Table 3.1 SystemVerilog extension to fork-join       | 24  |

|------------------------------------------------------|-----|

| Table 3.2 List of VMM Classes                        | 32  |

| Table 3.3 List of OVM Classes                        | 34  |

| Table 5.1 Registers used in Floating-point Adder     | 93  |

| Table 5.2 Features of VMM Pianner                    | 97  |

| Table 5.3 VMM Planner Run Commands                   | 98  |

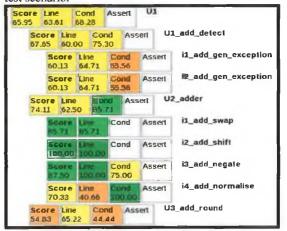

| Table 5.4 List of Test Cases                         | 105 |

| Table 5.5 List of tests run                          | 106 |

| Table 7.1 Formal Verification Tools                  | 175 |

| Table 7.2 Advantage & disadvantage of formal methods | 177 |

#### **Chapter 1 Introduction**

#### 1.1 Thesis Motivation

The continuous growth and complexity of digital design requires modern, systematic and automated approaches for creating test benches [1]. Given that up to 70% of the design time is spent in the verification process [5] it has become even more critical that verification engineers design test benches that are at the cutting edge of the verification industry.

The EDA vendors have recognised that a standardised approach for verification is required and this approach needs to support the structures needed to build an advanced verification environment. However, they don't actually specify how the architecture of the test bench environment should be built. It is still the verification engineer's responsibility to do this with the added pressure of making the environment re-usable for future chip sets.

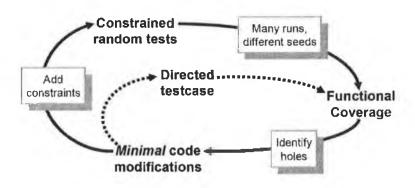

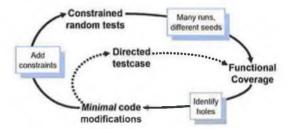

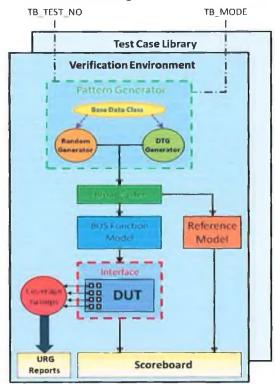

With this in mind the main goal is to develop a new and more effective intuitive way of designing test benches. This thesis describes the implementation of constrained random test stimuli, functional coverage, and assertions and also describes an approach for creating test cases that allow the use of both constrained random tests and directed tests within a single environment. The environment built should also have the capability to be easily modified where a Device Under Test (DUT) of similar structure can be verified.

The verification environment is built using SystemVerilog and VMM. SystemVerilog is the industry's first unified hardware description and verification language (HDVL). VMM provides a set of rules and recommendations for constructing test benches using SystemVerilog. This is done through a set of base classes which are used to describe important elements of the test bench

#### 1.2 Thesis Contributions

The contributions of this research are as follows:

- Summary of existing verification methodologies used in the Application Specific Integrated Circuit (ASIC) verification industry.

- Development of an advanced verification environment for a floating-point adder.

The DUT in this case has been provided by Chipright Ltd [29]. The environment has been developed using the SystemVerilog language and Synopsys's Verification Methodology Manual (VMM).

- Development of a Bus Functional Model (BFM) using SystemVerilog constructs to create an IEEE-754 compliant floating-point model for testing purposes.

- o Use of VMM Object Oriented (OO) base classes in the environment.

- Creation of a reference model to verify that the DUT has successfully implemented floating-point addition.

- Identification of functional coverage points inside the DUT and creation of a functional coverage plan

- Creation of functional coverage groups to collect data during simulations and analysis and comparison of the results with the functional coverage plan.

- Creation of assertions for the floating-point adder within the interface file.

- Verification of the adder using constrained random test stimuli in conjunction with the reference model.

- Collection of all functional coverage reports, assertion reports, sequencing reports and display in Hypertext Mark-up Language (HTML) format.

- Execution of simulations to obtain full verification of the adder model as determined by the functional coverage reports.

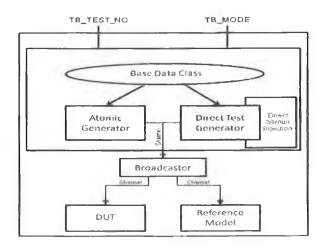

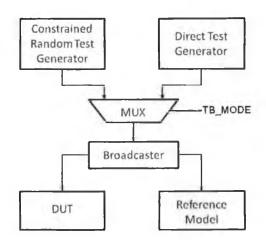

- Development of a test bench architecture that is structured to gain maximum efficiency from both constrained random and directed test case development.

- Extension of the verification environment to support a more complex BFM, thus proving that the testbench infrastructure can support both "intensive data verification" and more finely tuned "control of sequence and scenarios" verification.

- Investigation of the use of formal verification practices in the verification industry.

#### 1.3 Thesis Structure

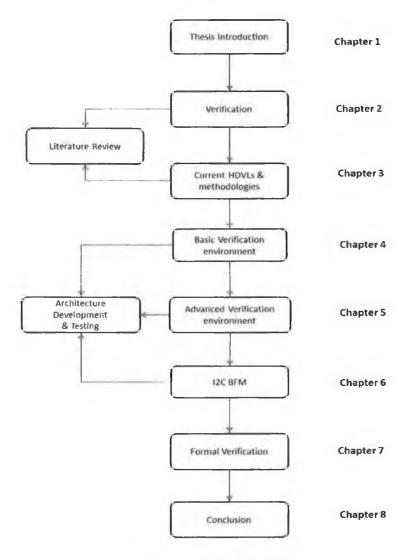

Figure 1.1 illustrates the steps taken throughout the project and the structure of the thesis.

Figure 1.1 Thesis Structure

The literature review carried out for this project is presented in chapter 2 and 3 of this thesis. The following areas were researched as part of a literature review.

Chapter 2 analyses the different types of verification techniques within ASIC verification. This chapter also describes the challenges associated with ASIC verification.

Chapter 3 reviews the different hardware and verification languages within the microelectronics industry. Also reviewed are Synopsys's VMM and Cadence/Mentor OVM and the different tools that support these methodologies.

Chapter 4 describes the implementation of a basic VMM based verification environment to test a floating-point adder. An IEEE-754 Floating-Point adder has been used as a case study in the implementation of a verification environment using the VMM methodology. The test bench has been written in the SystemVerilog language and includes the following elements:

- Constrainted random test stimuli to represent floating-point numbers

- A Bus Functional Model for the adder under test

- Assertions to check the design intent.

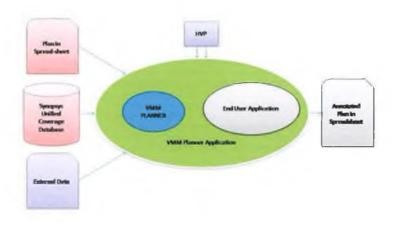

Chapter 5 outlines the architecture of the test environment. The test bench infrastructure is analysed and some key points are identified to yield a flexible solution that can meet industry level verification requirements. The chapter contains the test plan document that is used to help determine when the DUT has been completely verified. As part of the results analysis phase, the VMM Planner application from Synopsys is identified, described and used within the verification environment to ultimately help interpret the test results.

Chapter 6 describes how the verification infrastructure created and described within Chapter 5 can be re-used to facilitate the development of a more complex BFM. As part of a case study, the industry standardI2C protocol has been chosen. The BFM is built using the same template as outlined in Chapter4. This BFM is integrated into the verification environment and used to communicate with a DUT containing an I2C interface.

Chapter 7 describes the formal verification process and identifies how it is different to the constrained random approach undertaken in this project. As an added part of the research work, formal verification techniques have been reviewed with emphasis on determining if parts of this approach could be utilised within the advanced verification environment.

Chapter 8 outlines the results and conclusions of the research work. The key points of the research project are identified and discussed with recommendations for future research work.

#### Chapter 2 Review of ASIC Verification Techniques

#### 2.1Introduction

This chapter reviews ASIC Verification Techniques. Verification is the activity that determines the correctness of the design that is being developed. It ensures that the design meets the specification required of the product and the intent of which the product should operate [2].

Verification has become a major element within the digital design development process. Various industry surveys highlight that verification is the single largest component in a project, taking up more than half of the total project's staffing, schedule and cost [3]. It is often the limiting factor to project completion, and is becoming the single largest bottleneck in the ASIC industry.

Verification is complex, time-consuming, and sometimes poorly understood. As a result, the verification effort represents one of the bigger risks to the successful completion of a project.

This chapter gives an overview of what ASIC verification is and the importance of it within the microelectronics industry. Also described within this chapter are the challenges that verification has to overcome. A key point in explaining verification is that it is so vast and covers many areas within the electronics industry. Verification may be classified into three types: Applications, Software and Circuit Development. An example of each type is given below

#### **Applications:**

• File verification: Checks the formal correctness or integrity of a file

#### **Software Development:**

- Formal verification: Uses mathematical proofs to check the correctness of an algorithm

- Intelligent verification: Updates the testbench to changes in Register Transfer Level (RTL)

- Runtime verification: Verification technique that combines formal verification and program execution

- Software verification: Assures that software fully satisfies all of the requirements

#### Circuit Development:

- Functional verification: Verifies the design of digital hardware

- Analogue verification: Verifies analogue or mixed-signal hardware

- Physical verification: Verifies an IC layout design

The main verification techniques used within ASIC verification are functional verification and formal verification. Functional verification is the main verification type implemented throughout this project. Formal Verification is discussed from a research point of view in chapter 7.

#### 2.2The Goal of Verification

The goal of ASIC verification can be simply stated: to prove that a design will work as intended. There are four components to achieving this goal [3]:

- 1. Determine what the intent is

- 2. Determine what the design does

- 3. Compare the two to ensure that they match

- 4. Estimation of the level of confidence of the verification effort.

#### 2.2.1 Determining Intent

Determining the intent of the system is essential for verification to succeed [3]. The intent could be defined as what the system is supposed to do, which may be different from what it actually does.

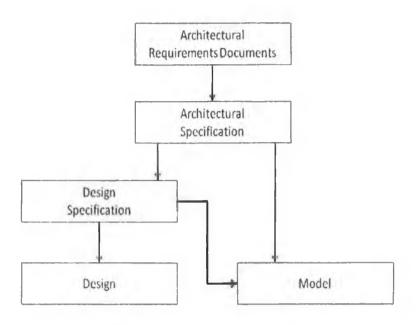

In some cases, the intent may be obvious, when it is possible to clearly specify the functions which the device must perform. However, for most reasonably complex digital systems even the intent may not always be clear. How should a device operate when an error is introduced, or when two competing actions are received at the same time, or when a resource is oversubscribed? It is often the architectural specification that describes the intent of the system and the implementation specification that documents how the design is intended to implement the intent as seen in figure 2.1.

The Architectural specification is usually created by examining many use-cases that are specific scenarios that describe how the device will work, and determining the system intent. The Architectural specification is defined to satisfy all of the use-cases.

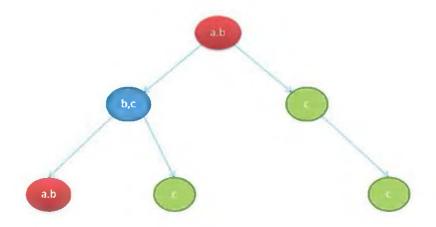

Figure 2.1 Specification Hierarchy

#### 2.2.2 Determining What a Design Does

The next part of ASIC verification is to determine what a design does. This is the first step in comparing the design with the intent. Since the design has not yet been implemented in a prototype, a model of the design is needed. The model is described in a software language that allows simulations to be run. The method used to test the model is quite traditional: stimulate it and see what happens. The poking is frequently referred to as stimulus injection, while the observation involves collecting and checking the outputs of the simulation.

#### 2.2.3 Comparing the Intent with the Design

Ideally, one would like to take the intent and the design, stimulate them in the same way, and check that the results match. This would provide a direct way to validate that the two are identical. The issue with this is that intent is not something that can usually be modelled. In some cases, it may not even be fully understood. Instead, something else must be used to represent the intent of the system. In some cases, people have built executable design specifications. That can be useful, but of course, the specification may also have errors. In other cases, the intent is captured as a reference model that is supposed to behave as the system is intended to work. These are some of the uses of the model block shown in figure 2.1. Still another is to provide a series of tests and

expected results to run against a design. These approaches, and most others, rely on comparing two different models, and examining the discrepancies. It is hoped that two models will not have exactly the same errors.

#### 2.2.4 Determining Verification Completeness

There are a number of other complexities that arise during the process of functional verification. One of the most frequently discussed is determining the completeness criteria of the verification.

Just as the system intent is often not fully defined, the design model may never be fully tested. There are several reasons for this. First, it is difficult to ensure that the complete intent of the system is known.

Anything that has not been included in the architectural specification or functional specification is unlikely to show up in the design or to be tested, even though the function may be required for the system to work. Secondly, it is difficult to know if the design has been tested sufficiently. Any issue that is found provides proof that the questions have not all been previously asked. It is rare that someone can prove that no other questions need asking. It is difficult to show that no more errors can be found. Another limitation of verification is the impracticality of running a complete test. Any reasonably sized design is too big to examine completely. Ideally an engineer wishes to see that all possible stimuli have been applied in all possible states of the design

As a result, functional verification is rarely certain and rarely complete. Given the importance of success to many verification projects, estimation methods are used to provide an approximation of the quality level of the functional verification.

#### 2.3 The ASIC Verification Challenge

Functional verification is a simple problem to state but a challenging one to address [4]. The increasing size and complexity of designs and shortening time to market means that verification engineers must verify larger and more complex design in a shorter time than in previous projects. An effective solution to meeting this increased demand for achieving verification closure must address the flowing verification challenges:

- Reusability

- Efficiency

- Productivity

- Code Performance

- Completeness

The challenge in **verification reusability** is to increase portions of the verification environment infrastructure that can be reused in another part of the project or in a completely different project [4]. This is done by sharing features that are similar with those in the current project. By using standardised interfaces or functions, a high degree of reuse can be achieved. Blocks can be reused in any project that makes use of the same standardised interface. As well as using standardised interfaces, identifying common functionality in the verification environment planning stage can lead to further reuse of verification infrastructure.

The challenge in verification efficiency is to minimise the amount of manual effort required for completing a verification project. The reason for reducing manual effort in a verification project is that it is error prone, omission prone and time consuming. In contrast, automated systems can complete a significant amount of work in a short time. However automated systems must be built manually. To improve verification efficiency, careful analysis is required of the trade-off between the extra effort required for building an automated system and the gains it affords. An example of such a system is the coverage driven random verification methodology where the effort to build an automated system for stimulus generation and automated checking leads to significant improvements in verification efficiency, and hence productivity. Before building an automated system an important consideration to be identified is that the automated

system requires a consistent infrastructure on which it can be developed, and also imposes a user model on how an engineer interacts with it. Deployment of an automated system requires consistency both in infrastructure and engineering approach, both of which take time and targeted effort to achieve.

The challenge in **verification productivity** is to maximise work produced manually by verification engineers in a given amount of time. Achieving higher productivity has become a major challenge in functional verification. Significant improvements in the design flow have afforded design engineers with much higher productivity. However improvements in verification productivity have lagged those on the design side, making functional verification the bottle neck in completing the design. The goal of functional verification is to reduce the gap between productivity and verification. To achieve this verification is moving to a higher level of abstraction and leveraging reuse concepts.

The challenge in **verification code performance** is to maximise the efficiency of verification programs. This consideration is in contrast with verification productivity, which deals with how efficiently verification engineers build the verification environment and verify the verification plan. The time spent on a verification project is usually dominated by the manual work performed by verification engineers. In most projects verification performance has usually been a secondary consideration to designing and building verification environments. An important area in which verification performance becomes a primary consideration is in running regression test suites where the turnaround times are dominated by how efficient verification programs operate. Expert knowledge of tools and languages used for implementing the environment is a mandatory requirement for improving verification performance.

The challenge in **verification completeness** is to maximise the part of the design behaviour that is verified. The major challenge in improving verification completeness is in capturing all of the scenarios that must be verified. This however is a manual, error prone, and omission prone process. There have been significant improvements in this area by moving to coverage driven methodologies. Coverage driven methodologies require a measure of completeness whose calculation requires strict planning, tracking and organisation of the verification plan. This strict requirement on verification plans naturally leads to exposing the relevant scenarios that may be missing. Fine-tuned

verification planning and management methods have been developed to help with the planning and tracking of verification plans.

#### 2.4 Functional Verification

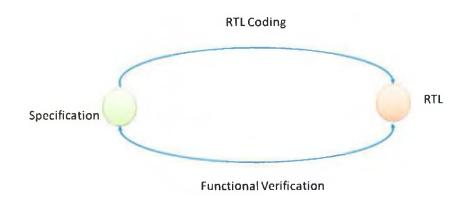

The main purpose of functional verification is to ensure that a design implements the intended functionality [5]. As shown by Figure 2.2, functional verification tries to establish a relationship between a design and its specification. Without functional verification, one must trust that the transformation of a specification into RTL code has been performed correctly, without misinterpretation of the specification's intent.

Figure 2.2 Functional Verification of the RTL with respect to the specification

It is important to note that, unless a specification is written in a formal language with precise semantics, it is difficult to prove that a design meets the intent of its specification. Specification documents are written using natural languages by individuals with varying degrees of ability in communicating their intentions. Any document is open to interpretation. One can easily prove that the design does not implement the intended function by identifying a single discrepancy. The opposite sadly, is not true: No one can prove that there are no discrepancies. Functional verification as a process can show that a design meets the intent of its specification, but it cannot prove it.

#### 2.4.1 Verification Process

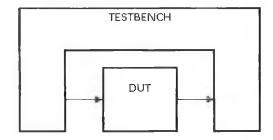

The process of verification should be primarily accomplished by placing the DUT in a testbench [3]. The testbench applies some test vectors to the design to ensure that the intent meets the specification. The testbench takes over the task of applying inputs (testcases) to the design and setting it up in a known configuration. Various input vectors are applied to the design to ensure that the response is as expected. In addition to the DUT, various other modules which check the output of the device or observe some signals of the DUT may also be instantiated in the testbench. These checkers could perform various functions in the testbench. For instance, some checkers may check for the correct signal sequence protocol on the inputs and outputs of the device. Monitors perform an additional function of watching the I/O or some specific busses in the DUT.

#### 2.4.2 What is a Testbench?

The term "testbench" usually refers to simulation code used to create a predetermined input sequence to a design and to observe the response [5]. Test benches are implemented using VHDL, Verilog, System C, SpecmanE, and System Verilog and may include external data files or C routines.

Figure 2.3 illustrates how a testbench interacts with a DUT. The testbench provides inputs to the design and watches any outputs. The verification challenge is to determine what input patterns to supply to the design and what is the expected output of a working design when subjected to those input patterns.

Figure 2.3 Testbench interaction with DUT

A testbench should be robust so that it provides a high level of confidence that the design being tested works correctly.

#### 2.5 The Bottleneck in ASIC Verification

Today in the era of multi-million gate ASICs and FPGAs, reusable intellectual property (IP), and system-on-a-chip (SoC) designs, verification can consume up to 70% of the design effort [5]. Design teams, properly staffed to address the verification challenge, include engineers dedicated to verification. The number of verification engineers can be up to twice the number of RTL designers.

#### 2.5.1 Reasons for the Verification Bottleneck

The verification bottleneck is a result of raising the design abstraction level for the following reasons [6]:

- Designing at a higher abstraction level allows engineers to build highly complex functions with ease. However, this increase in design complexity then results in almost doubling the verification effort. Doing so has doubled the functional complexity and hence its verification scope.

- Using a higher level of abstraction for design, transformation, and eventual mapping to the end product is not without information loss and misinterpretation. For instance, synthesis takes HDL-level design and transforms it to gate level format. Verification is needed at this level to ensure that the transformation is indeed correct, and that design intent has not been lost. Raising the level of abstraction also brings about the question of interpretation of the code that is used to describe the design during simulation.

Other factors that affect the verification problem are:

- Increase in functional complexity because of the complex nature of designs today; for example, co-existence of hardware and software, analogue and digital.

- The requirement for higher system reliability forces verification tasks to ensure that a chip level function will perform satisfactorily in a system environment, especially when a chip level defect has a multiplicative effect.

Research done by Collett International Research into functional verification by collecting information from design engineers shows some of the reasons behind the bottleneck in verification [7]. The result of their finding is shown below:

- Chip flaws because of design errors. 82% of designs with a re-spin resulting from logic and functional flows had design errors. This means that corner cases have not been adequately covered during the verification process and that bugs remain hidden in the design all the way through tape out.

- Chip flaws because of specification errors. 47% of designs with re-spin resulting from logic and functional flaws had incorrect or incomplete specification. 32% of designs with a re-spin resulting from logic and functional flaws had changes in specifications.

- Problems with reused IP and imported IP. 14% of all chips that failed had bugs in reused components or imported IP.

- Effects of a re-spin. Re-spins can cost a company up to \$100,000. In addition, a respin delays product introduction and adds to expense due to failing systems that use these defective chips.

#### 2.6 Conclusion

This chapter explains what verification is and some of the challenges and difficulties that are associated with it. One of the major problems mentioned in this chapter is the bottleneck within verification. To reduce the bottleneck in verification, companies have researched and developed solutions and ideas. Listed below are some of the ideas and solutions that companies have developed [7].

- 1. **Reduce chip complexity.** Practically, this is not possible because of customer demand for more functionality.

- Reduce the number of designs. This solution affects a company's long-term goal of being profitable.

- 3. Increase resources. Another alternative is to increase the number of designers or verification engineers. This alternative works well to some extent, but does not meet today's demands for verifying exponentially complex chips with a limited amount of time.

- 4. **Increase productivity of designers.** Productivity gains have been achieved by improving compute power, using personal tools such as Microsoft Excel. While they have been of great help in capturing test and verification plans, the majority of the time is spent in coding the test cases, running them, and debugging.

- 5. **Increase verification productivity.** This has obvious potential for gains in productivity.

To increase verification productivity, the EDA industry has come up with a solution similar to what was used to solve the design bottleneck - the concept of abstraction. Higher-level languages such as Verilog and VHDL support chip verification using test benches. These languages include constructs such as tasks, threading (fork, join) and control structures such as "while." This provides more control to fully exercise the design on all functional corners. However, these constructs are not synthesisable and hence are not used by designers as a part of actual design code.

As complexity continues to grow, new verification languages have been created and introduced that try to verify complex designs at various levels of abstraction. Along

with new verification languages, methodologies and tools have been developed to support them. One such verification language is SystemVerilog. Along with SystemVerilog the EDA companies have developed methodologies to support the language. The next chapter will discuss SystemVerilog and the different methodologies that support the language.

# Chapter 3 Current Verification Languages, Methodologies and Trends

#### 3.1Introduction

This chapter outlines the advantages SystemVerilog brings to the verification industry. SystemVerilog is a major extension of the established IEEE 1364 Verilog language [8]. These extensions are discussed, along with a review of the Verilog language. SystemVerilog also includes some features from the OpenVera verification language which is discussed in this chapter. Also explained are the different methodologies that have been developed by the major EDA companies to support SystemVerilog. Along with the methodologies the EDA companies are developing tools to support SystemVerilog.

#### 3.2 SystemVerilog

SystemVerilog is the industry's first unified hardware description and verification language (HDVL). SystemVerilog combines the features of Hardware Description Languages such as Verilog and VHDL with features from Hardware Verification Languages such as OpenVera. SystemVerilog also includes features from C and C++. SystemVerilog became an official IEEE standard (IEEE 1800) in 2005 [9]. It was developed originally by Accellera to improve productivity in the design of large gate count, IP based, bus intensive chips.

Since its development SystemVerilog is finding practical use in the areas of concise and productive RTL coding, assertion based verification, and building coverage driven verification environments using constrained random techniques

#### SystemVerilog provides:

- Constrained random stimulus generation

- Functional Coverage

- Assertion based Verification

- Higher-level structures, especially Object Oriented Programming

- Multi-Threading and inter-process communication

The methods listed above help to improve the verification process. SystemVerilog also provides enhanced hardware modelling features that improve the RTL design productivity and simplify the design process [10]. Since its development SystemVerilog has been adopted by hundreds of semiconductor design companies and supported by more than 75 EDA, IP and training solutions worldwide.

#### 3.3Verilog

SystemVerilog is a major extension of Verilog. Verilog is a hardware description language (HDL) used to model electronic systems. Verilog supports the design, verification and implementation of analogue, digital and mixed signal circuits at various levels of abstraction [11].

The designers of Verilog wanted a language with syntax similar to the C programming language. The language is case sensitive, it has a pre-processor like C, and the major control flow keywords such as "if" and "while" are similar to those in C.

Verilog differs from C in some fundamental ways. Verilog uses begin/end instead of curly braces to define a block of code. Verilog 1995 and 2001 do not have structures, pointers or recursive subroutines. However, SystemVerilog includes these capabilities. Also the concept of time, which is so important to a HDL, is not found in C.

The language differs from a conventional programming language in that the execution of statements is not strictly linear. A Verilog design consists of a hierarchy of modules [12]. Modules are defined with a set of input, output, and bi-directional ports. Internally, a module contains a list of wires and registers. Concurrent and sequential statements define the behaviour of the module by defining the relationships between component, ports, wires, and registers. Sequential statements are placed inside a begin/end block and executed in sequential order within the block. Concurrent statements and all begin/end blocks in the design are executed in parallel. A module can also contain one or more instances of another module to define sub-behaviour.

#### 3.4 OpenVera

OpenVera is an interoperable, open hardware verification language developed by Synopsys [13]. The OpenVera language has been used as the basis for the SystemVerilog IEEE Standard. OpenVera remains a widely adopted and well supported hardware verification language.

OpenVera is an intuitive easy to learn language that combines the familiarity and strengths of HDLs, C++ and Java, with additional constructs targeted at functional verification making it ideal for developing test benches, assertions and properties [14].

#### 3.5 History of Verilog and SystemVerilog

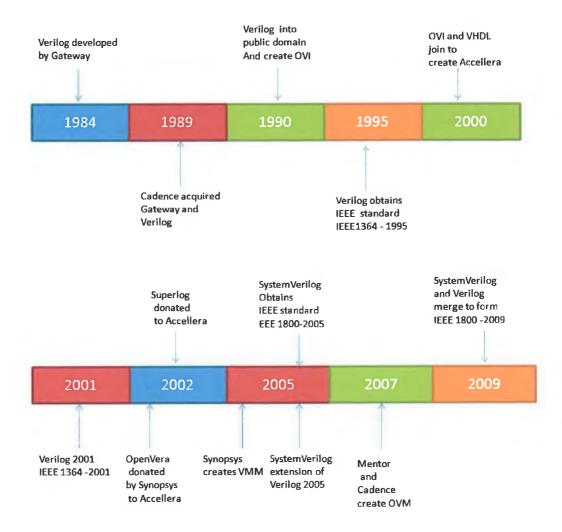

The Verilog Hardware Description Language (HDL) was originally developed together with the Verilog XL simulator by Gateway design automation and was introduced in 1984 [15]. In 1989 Cadence Design Systems acquired Gateway, and with it the rights to the Verilog language and the Verilog XL simulator. In 1990 Cadence placed the Verilog language into the public domain. Open Verilog International (OVI) is a non-profit organisation tasked with making Verilog an IEEE standard, achieved in 1995 (IEEE 1364 -1995). In 2000, OVI combined with Very High Speed Integrated Circuit (VHSIC) Hardware Description Language better known as VHDL to form Accellera. In 2001 a revised version of Verilog, known as Verilog 2001 was released, with the IEEE standard 1364 - 2001. This version incorporates many useful improvements. In 2002 Accellera introduced further extensions to Verilog and these were released under the name SystemVerilog 3.0. These extensions offer a higher level of abstraction for modelling and verification. An extended version of SystemVerilog 3.1 and a further revision of SystemVerilog 3.1a formed the basis for SystemVerilog obtaining an IEEE standard in 2005 (1800 - 2005). In 2009, the SystemVerilog and Verilog (IEEE 1394-2005) standard merged, creating the current IEEE Standard 1800-2009. Figure 3.1 illustrates the timeline of Verilog and SystemVerilog development.

Figure 3.1 Timeline of Verilog and SystemVerilog development

# 3.6 SystemVerilog Extensions to Verilog 2001

This section lists the major extensions and improvements and new features that SystemVerilog has made to Verilog 2001 [9].

The list of the extensions is included below along with a detailed explanation of each.

### **New Data Types**

One of the first improvements in SystemVerilog from Verilog is the different C like data types. The new data Types include byte, shortint, int, longint, bit, logic, string, chandle, typedef, struct, union, tagged union, enum.

## **Dynamic Data Types**

The next improvement in SystemVerilog is the use of dynamic data types. These include strings, classes, dynamic arrays, associative arrays including automatic memory management freeing users from de-allocation issues.

### Dynamic arrays:

One dimensional arrays whose size can be set or changed at runtime. The space for a dynamic array does not exist until the array is explicitly created at runtime.

### **Associative Array:**

When the size of the collection is unknown or the data space is sparse, an associative array is a better option than dynamic arrays. Associative arrays do not have the storage allocated until it is used, and the index expression is not restricted to integral expression, but can be of any type.

### Classes:

Classes are defined to support object oriented programming within SystemVerilog,. Classes consist of properties and methods. Classes may be extended to form a new class. This is called single inheritance. So basically classes are user defined data types. Classes may be instantiated to create objects. To support directed random verification,

Class Variables may be declared random. Classes may also include constraints, which direct the generation of random values.

## Built in methods to extend the language.

The next improvement in SystemVerilog is the built in methods to extend the language, e.g. array manipulation methods and enum and string methods. SystemVerilog also includes C like jump statements such as return, break and continue.

### **Enhanced Task and Functions**

SystemVerilog also enhances tasks and functions. In SystemVerilog, multiple statements can be written between the task declaration and end task, which means that begin / end, can be omitted. If begin / end is omitted, statements are executed sequentially. It is legal to have no statement at all.

## Extensions to fork - join

SystemVerilog also has extensions to fork-join to model pipelines and for enhanced process control. The fork- join construct enables the creation of concurrent processes from each of its parallel statements. A Verilog fork-join block always causes the process executing the fork statement to block until the termination of all forked processes. With the addition of the join\_any and join\_none keywords, SystemVerilog provides three choices for specifying when the parent resumes execution.

| Option    | Description                                                                                                                                                                               |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| join      | The parent process blocks until all the processes spawned by this fork complete                                                                                                           |

| join_any  | The parent process blocks until any one of the processes spawned by this fork complete                                                                                                    |

| join_none | The parent process continues to execute concurrently with all the processes spawned by the fork. The spawned processes do not start until the parent thread executes a blocking statement |

Table 3.1 SystemVerilog extension to fork-join

## **Extensions to the Always Block**

SystemVerilog provides extensions to the always block for modelling combinational, latched or clocked processes. In an always block which is used to model combinational logic, forgetting an else statement leads to an unintended latch. To avoid this mistake, SystemVerilog adds specialised always\_comb and always\_latch blocks, which indicate the design intent to simulation, synthesis and formal verification tools. SystemVerilog also adds an always ff block to indicate sequential logic.

### Interface

SystemVerilog adds interfaces to improve encapsulated communication. Interfaces may effectively be a "bundle of wires" with a single name, but they are also capable of containing behaviour and so may be used by BFMs. Interfaces therefore support Transaction Level Modelling (TLM) and in particular the reuse of verification environments at different levels of abstraction.

## **Clocking Block**

Clocking blocks allow control over the clocking behaviour of different parts of a testbench. Clocking blocks help the sampling of input/output data to be set up in a well-defined way [8].

### **Program Block**

Also included in SystemVerilog is the program block for describing tests. The program block is the basic building block in Verilog. The program block can contain hierarchies of other modules, wires, task and function declarations, and procedural statements within always and initial blocks [16]. This construct works extremely well for the description of hardware. However, for the testbench, the emphasis is not in the hardware level details such as wires, structural hierarchy, and interconnects, but in modelling the complete environment in which a design is verified. A lot of effort is spent getting the environment properly initialised and synchronised, avoiding races between the design and the test-bench, automating the generation of input stimuli, and reusing existing models and other infrastructure.

The program block serves three basic purposes:

- 1 It provides an entry point to the execution of test-benches.

- 2 It creates a scope that encapsulates program-wide data.

- 3 It provides a syntactic context that specifies execution in the Reactive region.

# **Direct Programming Interface (DPI)**

The SystemVerilog Direct Programming Interface (DPI) allows C functions to be called directly from SystemVerilog or vice versa without using the Programming Language Interface (PLI) [17]. The Direct Programming Interface (DPI) allows functions in a foreign language to be called as SystemVerilog functions. This is very useful as reference models are often written in C. They can then be used as a golden reference or as part of a checker in an automated testbench. The DPI allows this reuse in an efficient way.

## SystemVerilog Assertions (SVA)

#### What is an assertion?

An assertion is basically a "statement of fact" or "claim of truth" made about a design by a design or verification engineer [18]. An engineer will assert or "claim" that certain conditions are always true or never true about a design. If that claim can ever be proven false, then the assertion fails.

Assertions essentially become active design comments. Assertions can be checked dynamically by simulation, or statically by a separate property checker tool i.e. a formal verification tool that proves whether or not a design meets its specification. Such tools may require certain assumptions about the design's behaviour to be specified.

## What is a property?

A property is basically a rule that will be asserted to passively test a design [18]. The property can be a simple Boolean test regarding conditions that should always hold true about the design, or it can be a sampled sequence of signals that should follow a legal and prescribed protocol.

For formal analysis, a property describes the environment of the block under verification, i.e. what is the legal behaviour of the inputs.

## Types of SystemVerilog Assertions:

### **Immediate Assertions**

Immediate assertions are procedural statements and are mainly used in simulation. An assertion is basically a statement that something must be true, similar to the *if* statement. The difference is that an *if* statement does not assert that an expression is true, it simply checks that it is true.

```

if (A==B) // Simply checks if A equals B

assert (A == B) // Asserts that A equals B; if not an error

is generated

```

Figure 3.2 Example of Immediate Assertion

### **Concurrent Assertions:**

The most valuable assertion style that can be used in design and verification environments is the concurrent assertion. Concurrent assertions are monitors that reside inside a block of code to periodically sample and test signals and to generate error messages if the assertion ever fails. Concurrent assertions are typically sampled once per clock period at the end of the clock cycle, just before the next active clock edge. Concurrent assertions require the assertion of a property, where a property is basically a design rule that should always be true. The simplest of concurrent assertions takes the form:

```

assert property (!(Read && Write));

// asserts that the expression Read && Write is never true at any point during simulation.

```

Figure 3.3 Example of Concurrent Assertions

Properties may be checked using concurrent assertions. If an asserted property does not hold, the assertion is violated and an error is generated, Assertions may be checked dynamically during simulation, or statically using a property checker, which is a type of formal verification tool.

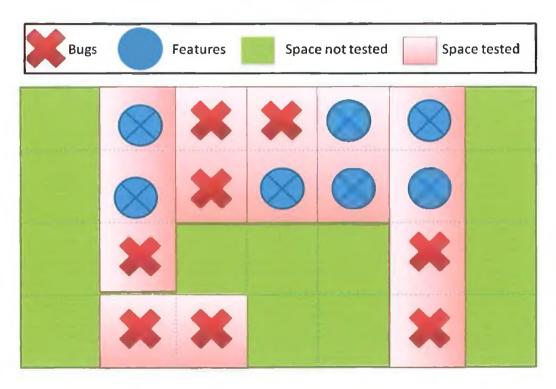

## Coverage

Coverage serves two critical purposes throughout the verification process [19]. The first is to identify holes in the process by pointing to areas of the design that have not yet been sufficiently verified. This helps to direct the verification effort by answering the key question of what test to write next (directed test or constrained random test).

Coverage is also an indicator of when verification is thorough enough to tape out the design. Coverage provides more than a simple yes/no answer; incremental improvement in coverage helps to assess verification progress and thoroughness, leading to the point at which the development team has the confidence to tape out the design. In fact, coverage is so critical that most advanced, automated approaches implement coverage driven verification, in which coverage guides each step of the process.

Coverage is divided into two main categories: code coverage and functional coverage. Code coverage, in its many forms (line coverage, toggle coverage, expression coverage), is typically an automated process that tells whether all of the code in a particular RTL design description was exercised during a particular simulation run (or set of runs). Code coverage is a necessary but not sufficient component of a reliable verification methodology.

In contrast, functional coverage provides an explicit metric of how much of the desired functionality of the design has actually been exercised. Verification confidence can often be improved further by using cross-coverage techniques to measure combinations of coverage metrics [19]. Important functional coverage and cross-coverage points should be identified early in the project and preferably included in the written verification plan.

The process of filling the holes identified by the full range of coverage is the heart of the coverage driven verification process. When 100% coverage is achieved then the verification confidence is high enough to tape out the design. SystemVerilog provides coverage properties for lower level coverage points, covergroups for tracking higher level values and support for cross coverage.

### **Object Oriented**

SystemVerilog provides an object-oriented programming model [20]. SystemVerilog classes support a single inheritance model. There is no facility that permits conformance of a class to multiple functional interfaces, such as the interface feature of Java. SystemVerilog classes can be type parameterised, providing the basic function of C++ templates. However, function templates and template specialization are not supported.

The polymorphism features are similar to those of C++: the programmer may specifically write a virtual function to have a derived class gain control of the function.

Encapsulation and data hiding is accomplished using the local and protected keywords, which must be applied to any item that is to be hidden. By default, all class properties are public.

SystemVerilog class instances are created with the new keyword. A constructor denoted by function new () can be defined. SystemVerilog supports garbage collection, so there is no facility to explicitly destroy class instances.

## 3.7 Methodologies and Tools

Since the release of SystemVerilog in 2002 the key EDA companies Synopsys, Mentor Graphics and Cadence have been developing methodologies to support the language. Synopsys were the first to develop a successful methodology for SystemVerilog called Verification Methodology Manual (VMM) in 2005. Mentor developed an open source methodology called Advanced Verification Methodology (AVM) in 2005. Cadence in 2006 also developed a methodology for SystemVerilog called Universal Reuse Methodology (URM). Since 2005 a number of changes and developments have been made to the methodologies. In 2007 Mentor and Cadence came together and formed a new methodology called Open Verification Methodology (OVM) that was also open source. Since OVM's development Synopsys have made VMM open source in 2008 and in 2009 released a new version of VMM (VMM 1.2) that has similar features to OVM. In late 2008 Mentor announced the availability of an open-source SystemVerilog solution (interoperability library) for users of OVM. The solution enables the easy and flexible reuse of VMM code within an OVM environment.

## What is Interoperability?

VMM based verification components can now be seamlessly reused within an OVM environment [21]. In addition, entire VMM environments can be reused without modification within an OVM environment through the use of the Interoperability library that provides the data and semantic conversions between the old and new environments.

# 3.7.1 Verification Methodology Manual (VMM)

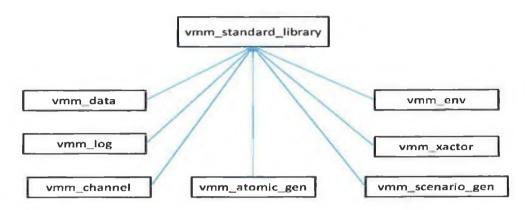

VMM is co-authored by verification experts from ARM and Synopsys. VMM describes how to use SystemVerilog to develop scalable, predictable and reusable verification environments [22]. VMM has become an important factor in increasing verification reuse, improving verification productivity and timelines. VMM consists of coding guide lines and base classes. VMM is focused on coverage driven verification (CDV).

VMM libraries consists of the following sub libraries

- VMM Standard Library

- VMM Register Abstraction Layer (RAL)

- VMM Hardware Abstraction Layer (HAL)

The VMM Standard Library provides base classes for key aspects of the verification environment, transaction generation, notification service and a message logging service.

| VMM<br>Component | Description                                                                                                                                                                                                                                           |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| vmm_env          | The class is a base class used to implement verification environments.                                                                                                                                                                                |

| vmm_xactor       | This class is to be used as the basis for all transactors, including bus functional models, monitors and generators. It provides a standard control mechanism expected to be found in all transactors.                                                |

| vmm_channel      | This class implements a generic transaction level interface mechanism. The transaction level interfaces remove the higher level layers from the physical interface details. Using vmm_channel, transactors can pass transactions from one to another. |

| vmm_data         | This class is to be used as the basis for all transaction descriptors and data models. It provides a standard set of methods expected to be found in all descriptors. The user must extend vmm_data to create a custom transaction.                   |

| vmm_log          | This class provide a mechanism for reporting simulation activity to a file or a terminal. The vmm_log class ensures a consistent look and feel to the messages issued from different sources.                                                         |

| vmm_atomic_      | vmm_atomic_gen is a macro. This macro defines an atomic generator for generating transactions which are derived from                                                                                                                                  |

| gen                  | vmm_data.                                                                                             |

|----------------------|-------------------------------------------------------------------------------------------------------|

| vmm_scenario_<br>gen | Defines a scenario generator class to generate sequences of related instances of the specified class. |

Table 3.2 List of VMM Classes

Figure 3.4 VMM Standard Library

## 3.7.2 Open Verification Methodology (OVM)

The OVM is the result of joint development between Cadence and Mentor Graphics. OVM is open source; it combines features from URM and AVM. The OVM Class Library [23] provides the building blocks needed to quickly develop well-constructed and reusable verification components and test environments in SystemVerilog.

# The OVM library contains

- Component classes for building testbench components like generator, driver, monitor

- · Reporting classes for logging,

- Factory for object substitution.

- Synchronisation classes for managing concurrent process.

- TLM Classes for transaction level interface.

- Sequencer and Sequence classes for generating realistic stimulus.

- Macros which can be used for shorthand notation of complex implementation.

| Ovm Component | Description                                                                                                                                                                                                                           |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ovm_driver    | Driver takes the transaction from the sequencer using seq_item_port. This transaction will be driven to DUT as per the interface specification.                                                                                       |

| ovm_env       | Used to create and connect the ovm_components like driver, monitors, sequencers etc. An environment class can also be used as sub-environment in another environment.                                                                 |

| ovm_test      | Using ovm_test provides the ability to select which test to execute using the OVM_TESTNAME command line option or argument to the ovm_root::run_test task.                                                                            |

| ovm_sequencer | Sequencer generates stimulus data and passes it to the driver. All sequencers should be derived from the ovm_sequence base class directly or indirectly. ovm_sequence base call is parameterised for request and response item types. |

| ovm_monitor   | ovm_monitor allows you to distinguish monitors from generic component types inheriting from ovm_component.                                                                                                                            |

| ovm_scoreboard        | ovm_scoreboard will allow you to distinguish scoreboards from other component types inheriting directly from own component.                                                                                                                                                                                         |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ovm_transaction       | The ovm_transaction class is the root base class for OVM transactions. Inheriting all the methods of ovm_object, ovm_transaction adds timing and recording interface.                                                                                                                                               |

| ovm_sequence_<br>item | The ovm_sequence_item class provides the basic functionality for objects, both sequence items and sequences, to operate in the sequence mechanism.                                                                                                                                                                  |

| ovm_sequence          | A sequence is defined by extending ovm_sequence class. This sequence of transactions should be defined in body() method of ovm_sequence class. OVM has macros and methods to define the transaction types                                                                                                           |

| ovm_object            | The ovm_object class is the base class for all OVM data and hierarchical classes. Its primary role is to define a set of methods for such common operations as create, copy, compare, print, and record. Classes deriving from ovm_object must implement the pure virtual methods such as create and get_type_name. |

Table 3.3 List of OVM Classes

Figure 3.5 OVM Library

## 3.7.3 Synopsys VCS Comprehensive RTL Verification Solution

VCS [24] is an RTL verification product that provides advanced bug finding technologies with a built in debug and visualisation environment. VCS supports all popular design and verification languages including Verilog, VHDL, SystemVerilog and SystemC. VCS includes the full featured native testbench, complete assertions and comprehensive code and functional coverage making bug finding faster and easier. Also VCS Verification Library provides verification IP for today's most popular bus standards.

# **Key Benefits**

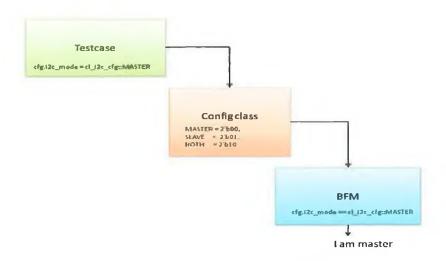

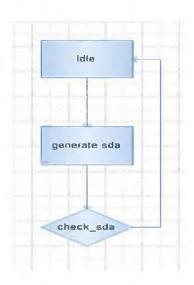

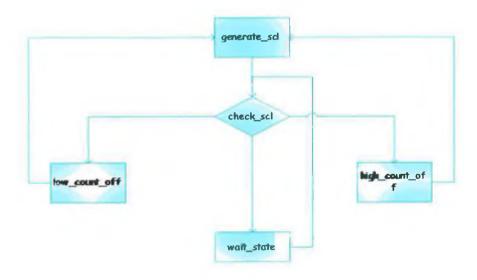

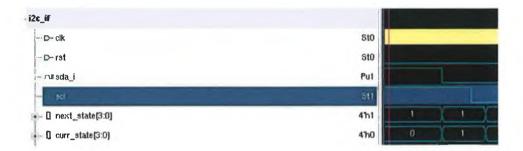

- Supports SystemVerilog and OpenVera test benches.